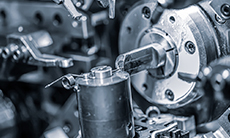

미래 반도체 제조공정의 핵심 기술이 개발됐다. 차세대 반도체 소재를 원자층 수준에서 정밀하게 쌓는 기술이다. 낮은 온도에서도 나노 수준의 3차원 구조에 적용 가능해 다양한 전자 소자에 활용될 전망이다.

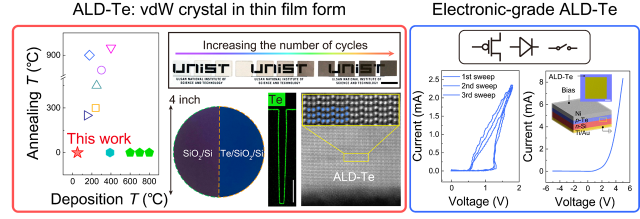

유니스트(UNIST·울산과학기술원) 반도체 소재·부품 대학원 및 신소재공학과 서준기 교수팀은 홍익대학교 송봉근 교수, UNIST 정후영 교수 연구팀과 함께 원자층 증착법(Atomic layer deposition, ALD)으로 50℃에서 텔레륨(Tellurium) 원자가 규칙적으로 배열되는 박막 증착 공정법을 개발했다고 1일 밝혔다.

원자층 증착법은 낮은 공정온도에서 삼차원 구조의 표면에 얇고 균일한 막 코팅과 정교한 두께 조절이 가능한 차세대 박막 공정법이다. 하지만, 차세대 반도체인 원자층 반도체에 적용하기 위해선 일반적으로 250℃ 이상의 공정온도와 450℃ 이상의 추가 열처리 작업이 요구된다.

연구팀은 전자소자, 열전소재 등의 다양한 분야에서 연구 중인 단일 원소 원자층 반도체 ‘텔레륨’에 원자층 증착법을 적용했다. 열처리 공정 없이도 50℃의 저온에서 고품질의 박막을 성공적으로 제조했다. 제조된 박막은 원자가 규칙적으로 배열되고, 나노미터(10억분의 1m)이하의 두께 조절이 가능하며 모든 표면 위에서 균일하게 증착됐다.

연구팀은 낮은 온도에서 반응성을 향상시키기 위해 산-염기성을 갖는 두 가지의 전구체 화학반응을 통해 특정 물질을 제조하기 위해 사용되는 화학 원료를 활용했다. 높은 표면반응과 안정성을 위한 물질인 공반응물을 추가 활용하고, 전구체를 더 짧은 간격으로 분할 반복 주입했다. 밀도가 낮고 불연속적인 알갱이가 증착되는 기존 방식에 비해 촘촘하고 밀도 높은 박막을 성공적으로 제조할 수 있었다.

개발된 제조공정을 통해 텔레륨 박막을 4인치(100㎜) 웨이퍼 전체에 적용했다. 박막은 원자층 수준의 두께 조절과 균일한 증착이 가능했다. 소자의 고집적화를 위해 요구되는 수직형 삼차원 구조체에도 증착 가능함을 확인했다. 이는 트랜지스터, 정류기, 선택소자 등의 다양한 전자 소자에 활용될 수 있다.

제 1저자인 김창환 연구원은 “이번 연구는 기존 박막 증착법의 한계를 극복하고 텔레륨을 원자층 증착법이라는 새로운 증착 방식을 구현했다”며 “텔레륨 박막은 복잡한 삼차원 소자 구조에서도 균일하게 증착할 수 있어 다양한 전자 소자에 응용이 가능할 것이다”고 전했다.

서준기 반도체 소재·부품 대학원 및 신소재공학과 교수는 “이번 연구는 저온, 대면적, 고품질 합성이라는 반도체 증착 공정에서 요구되는 모든 키워드들을 만족시킬 수 있었다”며 “전통적인 증착법에 새로운 공정 요소들을 더해 ‘비전통적인’ 이차원 신소재 및 신소자 구현에 성공했다는 점에서 다양한 응용 연구가 가능할 것”이라고 전했다.

이번 연구는 7월 11일 나노과학 분야 국제 학술지 ‘ACS Nano’에 온라인 게제됐고 우수한 성과를 인정받아 표지논문으로 선정됐다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

jjs@sedaily.com

jjs@sedaily.com