반도체 기본소자 제조 '나노 SOI' 기술 개발<br>전력소비 2~4배 감소·수백 GHz 전송속도 가능<br>세계 최고 수준 平… 2010년께 상용화 목표

| | 박재근(가운데) 교수와 한양대 나노 SOI 공정연구실 연구진. 세계 최고의 나노 SOI 공정기술을 개발, 한국 반도체 산업을 한단계 업그레이드 시킨 것으로 평가된다. |

|

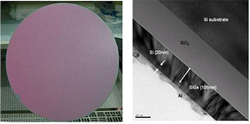

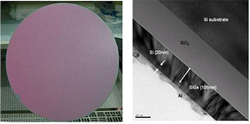

| | 300㎜ 고성능 나노 SOI 웨이퍼 및 구조 |

|

2일 ‘이달의 과학기술자상’ 11월 수상자로 선정된 박재근 한양대 전자통신컴퓨터 공학부 교수는 차세대 반도체 소자 핵심 기반 기술인 나노미터급 SOI(Silicon on Insulator) 기술을 개발한 공로다.

이 기술은 차세대 정보통신 반도체용 CPU(중앙처리장치)와 MPU(초소형 연산처리장치)을 구성하는 기본 소자 제조기술로 수백㎓(기가헤르츠)의 동작속도와 초저전력 특성을 나타내며 테라비트급 메모리 소자의 기본 소자로서도 적용될 예정이다.

현재 메모리나 SOC, 마이크로 프로세스용 등 소자구조는 실리콘(Si) 덩어리만을 사용하는 벌크 실리콘 웨이퍼 기반구조를 가지고 있어 낮출 수 있는 전력소모량이나 고속화 면에서는 한계에 도달한 것으로 지적됐다.

이를 극복하기 위해 최근 맹렬히 연구되고 있는 것이 실리콘과 절연체를 번갈아서 붙인 SOI 기반 소자구조다.

SOI는 두개의 실리콘층 사이에 100㎚ 정도 두께의 절연체(InsulatorㆍSiO₂)가 삽입된 모양을 하고 있는 데 상층 실리콘의 두께가 얇을수록 CPU 등의 동작속도를 빨리 할 수 있다. 박 교수팀은 이번에 상층 실리콘을 세계 최초로 30㎚ 이하 두께로 만드는 데 성공한 것이다.

박 교수팀 이전의 SOI 기술로는 크게 산소이온 주입과 고온 열처리 공정으로 제조하는 사이목스(SIMOX) 방법 및 수소이온 주입 및 결합 후 고온 열처리를 통해 분리하는 스마트컷(Smart-cut) 기술 등이 주로 사용됐다.

하지만 이 방식으로는 상층부 실리콘 두께가 50㎚ 이하의 SOI 구조가 불가능했으며 특히 고온 프로세스를 사용하기 때문에 응력 실리콘, 이완 실리콘저마늄, 산화막, 실리콘 복합층 구조를 가진 고성능 나노 SOI 웨이퍼를 제조할 수 없었다..

이에 대해 박 교수팀이 개발한 고성능 나노 SOI 공정 기술은 ▦저온에서 나노 두께의 실리콘을 성장시키는 나노 에피 실리콘 성장기술 및 나노 복합 실리콘저마늄층 성장기술 ▦나노층 분리기술 ▦무결정 결함 결합 기술 ▦나노 표면 처리기술 ▦나노 소자 제조기술 등 모두 5개의 핵심기술을 통해 최소 5㎚ 두께 크기의 소자를 만드는 데 성공했다.

특히 각 단위의 공정기술을 개발한 것과 아울러 개발된 단위 공정을 상호 융합시킴으로써 보다 효율적으로 작동하게 했다.

이번 나노 SOI 공정 기술은 기존의 기판 실리콘 대비 전력소비 2~4배 감소, 알파입자에 의해 야기되는 에러인 소프트에러율을 2~3배 감소 등의 효과가 있을 것으로 평가된다.

특히 수백㎓의 전송속도가 가능하게 됐고 박 교수팀은 이를 국내 실리콘 웨이퍼 제조업체인 LG실트론에 양산기술을 이전하면서 오는 2010년 상용화를 목표로 하고 있다.

산업의 쌀이라 일컬어지는 반도체 산업은 국가 기간산업의 핵심 중의 핵심이다. 반도체 제조기술은 다양한 분야의 기술이 요구되면 특히 설계, 제조공정, 프로세스, 테스트, 조립 기술 등 지금까지 국내 반도체 업계가 세계 시장을 주도해 왔다.

다만 원자재 및 공정설비 등에서는 해외 의존도가 높아 해외 경쟁사 및 경쟁국의 견제를 받아 이에 대한 기술 개발이 시급히 요구돼 왔다.

나노 SOI 소자구조도 이미 5년 전부터 미국의 IBM사가 고속 마이크로프로세서에 적용해 이 분야 기술을 선도해 왔다. 이와 함께 인텔이나 AMD, 모토롤라, 일본의 일본전기 등의 선진국 기업들이 기술개발을 위해 전력을 경주하고 있는 상황이다.

국내 반도체 기술은 그동안 이들보다 2년 정도 뒤쳐진 상태로 평가됐지만 이번 박 교수팀의 30㎚급의 성공으로 이들 기업들을 단번에 제쳤다.

또 고성능 나노 SOI 공정기술 개발은 국내 반도체 산업이 제조기술 및 재료 디자인 기술까지 보유하게 됨으로써 명실상부한 세계적인 반도체 기술 우위 국가로 위상을 드높인 것으로 평가를 받고 있다.

한편 이번에 개발된 나노 SOI 공정기술은 꿈의 디스플레이인 투명하고 휘어지는 실리콘 트랜지스터가 장착된 디스플레이 개발에 필요한 핵심 기반 기술로 적용됐으며 현재 초고해상도의 마이크로 디스플레이를 개발 중에 있다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >