|

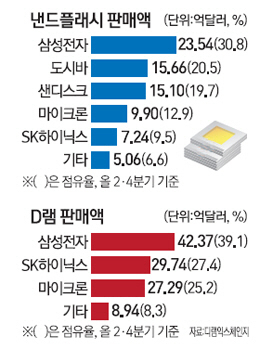

메모리 반도체 업체들의 기술 경쟁이 미세 공정에서 적층(積層)으로 옮아가고 있다. 회로 선폭을 줄이는 미세 공정 기술이 14나노미터(nm·1나노미터는 10억분의 1m)대까지 진입하면서 구조적 한계에 다다르자 셀을 수직으로 쌓은 적층기술을 통해 성능 향상을 꾀하고 있다. 특히 3차원(3D) 낸드와 같이 메모리 셀을 얼마나 높이 안정적으로 쌓을 수 있느냐에 따라 업체 간 명암이 엇갈릴 것이라는 전망이 나온다.

15일 업계에 따르면 삼성전자는 최근 14.3나노미터 낸드플래시 개발을 끝내고 미세 공정 목표를 14.2나노로 수정했다. 반도체에서 나노는 회로선폭의 크기를 나타내며 작을수록 성능이 뛰어나고 생산원가도 낮기 때문에 업체들은 미세 공정에 투자를 늘려왔다.

삼성전자는 D램의 경우 2010년부터 매년 40→ 30→ 28 →25나노로 줄여왔고 지금은 20나노 D램을 양산 중이다. 2000년대 중반 40나노급에 머물던 낸드 공정은 현재 16나노급까지 세밀화됐다.

업계에서는 14나노를 사실상 낸드 미세화의 마지막 단계로 보고 있다. 10나노 낸드 개발이 기술적으로는 가능해도 장비 등 추가 투자비 등을 고려하면 수익을 내기 어렵다는 판단에서다.

회로선 폭을 줄이는 방식으로 반도체를 작고 세밀하게 만들면 웨이퍼 1장 당 더 많은 칩을 생산할 수 있지만 미세 공정으로 셀 간격이 좁아져 데이터 안정성을 저해하는 간섭 현상 등 한계도 드러냈다. D램 역시 미세화 정도가 높아질수록 구조가 불안정해지는 단점이 있다. 삼성전자가 낸드 미세 공정 개발 목표치를 0.1나노 정도로만 수정한 것도 이와 무관치 않다는 분석이다.

미세 공정이 어느 정도 한계치에 다다르자 업체들은 기존 평면구조의 셀을 수직으로 쌓은 3차원(3D) 반도체로 돌파구를 열고 있다. 3D 반도체는 평면구조에 비해 용량과 내구성, 전력효율을 획기적으로 높일 수 있어 매력적이다.

3D 메모리 반도체의 관건은 셀을 안정적으로 높이 쌓는 기술력이다. 현재 가장 앞선 곳은 삼성전자다. 지난해 8월 세계 최초로 24층짜리 3D V낸드의 양산을 발표한데 이어 지난 5월에는 32층 V낸드를 출시했다. 3D V낸드의 양산은 삼성전자가 유일하다. 업계 일각에서는 삼성이 이미 48층 V낸드의 개발을 완료했을 것이란 관측도 나온다. 지난달 27일에는 실리콘관통전극(TSV) 기술을 적용한 3D D램도 세계 최초로 내놓으며 시장을 주도하는 모습이다.

일본의 도시바도 3D 낸드용 설비 확보를 위해 오는 2016년까지 제2제조동을 준공할 계획으로 있는 등 투자를 늘리고 있다. 도시바는 40~70층짜리 V낸드 양산을 목표로 삼고 기술경쟁을 예고하고 있다. SK하이닉스도 올해 안에 3D 낸드의 양산을 시작하겠다고 밝힌 상태다. 반도체 전문가들은 수년 뒤 100층까지 쌓은 제품이 나올 수 있을 것으로 전망하고 있다. 이상언 KB투자증권 분석가는 "삼성의 기술은 안정성이 강점이고 도시바는 효율적으로 셀층을 쌓는다는 강점이 있다는 게 대체적인 평가"라며 "아직 개발 초기인 만큼 승패를 가리기는 이르다"고 말했다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >