현재 스마트폰이나 TV 등에서 기본 소자인 상보형금속산화반도체(CMOS)회로를 구성하기 위해서는 반드시 n형 반도체와 p형 반도체가 필요하다.

n형과 p형 반도체는 각각의 특성이 달라 별개의 기판에 성형해야 하기 때문에 공정 횟수가 증가하는 것은 물론, 패터닝(Patterning)이 어려워 양산 비용도 높다는 문제점이 지적돼 왔다.

하지만 양극성 물질인 유기반도체는 극성 조절에 따라 n형과 p형반도체 양쪽 모두에 사용될 수 있어, 이 특성을 이용하면 복잡한 전자소자를 하나의 물질로 만들어 공정가격을 획기적으로 낮출 수 있다.

그렇지만 지금까지 개발된 유기반도체 극성 조절기술은 특정한 시스템에만 적용 가능해 대면적을 저가에 생산하는 데는 한계가 있었다.

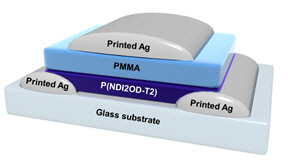

한국생산기술연구원 메카트로닉스융합기술그룹 김혁 박사와 서울대학교 반도체공동연구소장 이창희 교수가 이끄는 공동 연구팀이 잉크젯 프린팅 공정을 도입, 찍어내듯 CMOS 회로를 생산해 저가로 대면적을 생산할 수 있는 공정기술을 개발, 반도체 공정비용을 50%이상 절감시키는데 성공했다.

전하 주입량을 제어하는 기술을 개발해 한 가지 물질로 높은 성능을 구현했으며, 이에 따른 반도체 내부의 전하 농도 조절도 가능해져 유기반도체의 극성을 자유자재로 바꾸며 다양한 시스템에 적용할 수 있게 됐다.

김혁 박사는 “자율주행차, 인공지능, 사물인터넷 등 첨단기술의 핵심부품으로 반도체가 사용되면서 수요가 늘고 있다”면서, “이번 기술개발로 차세대 반도체로 주목 받고 있는 유기 반도체가 더욱 폭넓게 사용돼 그 수요에 부응할 수 있을 것”이라고 밝혔다.

한국연구재단 중견연구지원사업 도약연구와 산업통상자원부에서 추진하는 산업핵심기술개발사업으로 수행된 이번 연구는 네이처가 발행하는 자매지 사이언티픽 리포츠 4월 12자 온라인판에 게재됐다. 또 현재 1편의 국내 특허출원 완료 후 해외 특허출원 중에 있다.

/문병도기자 do@sedaily.com

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >