'TSMC, 너는 계획이 다 있구나' 1편에서는 이 회사가 VLSI 2022에서 발표했던 차세대 트랜지스터 구조 CFET, 채널·소스와 드레인·배선 공정 변화를 살펴봤습니다. 2편에서는 TSMC가 패키징 실력에 얼마나 자신있는 태도를 가지고 있는 지에 대해 살펴보려고 합니다. 출발해봅시다.

◇패키징, TSMC의 자존심으로 '우뚝'

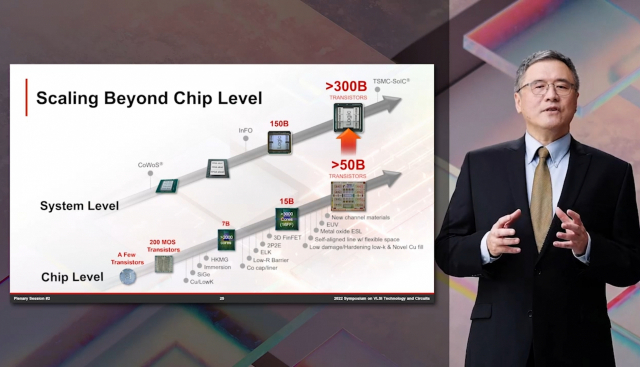

VLSI 2022 발표자 미위졔 TSMC 수석부사장은 기조연설 발표 시간 중 거의 절반 가량을 패키징 사업 소개에 할애했습니다.

최근 반도체 업계에서는 공정 한계로 한 개 칩에 트랜지스터를 욱여넣는 게 힘들어지자, 서로 다른 칩을 한 개처럼 이어붙이는 패키징 기술이 대세로 떠오르고 있죠. 이종결합(異種結合), '헤테로지니어스'라는 말이 유행처럼 번지고 있습니다.

TSMC는 이 분야에 상당히 투자를 많이 하는 모습입니다. 미래 파운드리 시장에서도 리더십을 이어가기 위해 전력투구하겠다는 의지로 읽히는데요.

이미 강해령의 하이엔드 테크에서는 'TSMC 패키징 특집: 내가 패키징 왕이 될 상인가' 편에서 이 회사의 로드맵을 자세히 다뤄봤습니다. 하이브리드 본딩 등에 대한 용어가 궁금하시다면 기사를 검색해주세요. 이번 편에는 다양한 TSMC의 패키징 제품군 가운데 흥미로운 부분 딱 하나만 짚어볼게요.

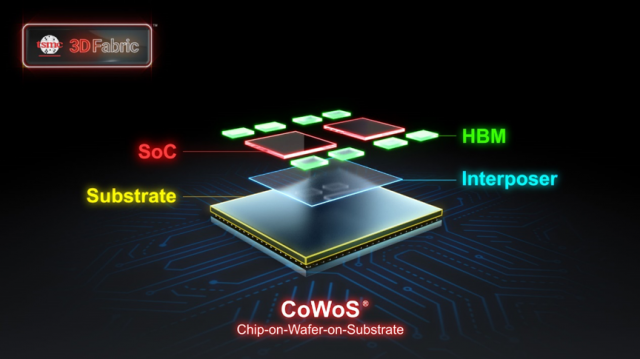

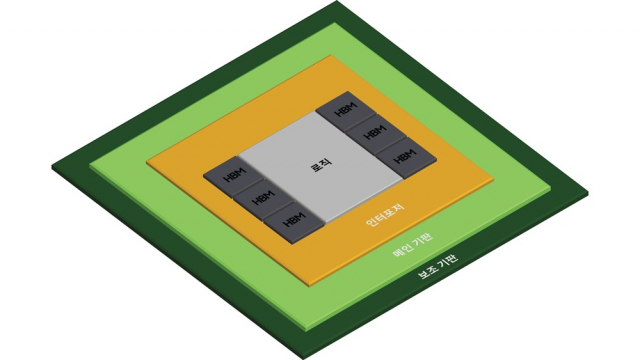

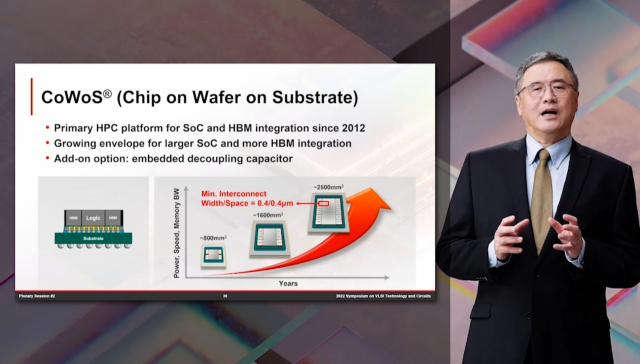

이 발표 자료 가운데 'CoWoS'라는 패키징 제품군을 흥미롭게 볼 만 합니다. CoWoS는 '칩온 웨이퍼온 서브스트레이트'의 줄임말입니다. 용어가 길어도 그림을 보면 어렵지 않습니다. 그림과 함께 보시죠.

CoWoS는 IT 기기의 '두뇌' 역할을 하는 중앙처리장치(CPU)나 그래픽처리장치(GPU)를 기판 중앙에 올려놓고, 고대역폭메모리(HBM)를 가장자리에 배치하는 기술인데요. HBM은 D램 칩을 여러 개 수직으로 쌓은 제품입니다. 기존 D램 모듈보다 연산 속도가 상당히 빠른 차세대 D램으로 손꼽히는데요. 이런 형태라면 기존 D램 모듈을 슬롯 형태로 배치했을 때보다 거리, 대역폭이 개선돼 데이터 병목 현상이 획기적으로 줄어듭니다.

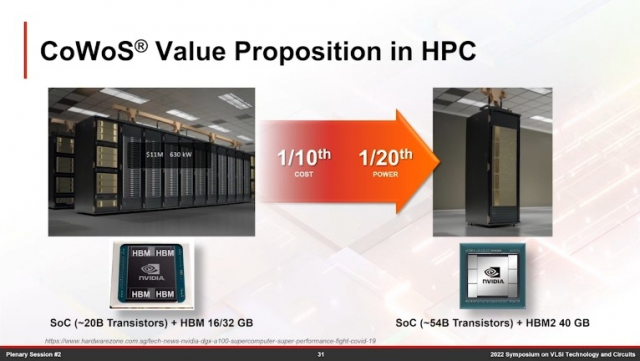

미위졘 수석부사장은 TSMC의 CoWoS 기술을 소개하면서 주요 고객사인 엔비디아 사례와 함께 장표를 제시합니다. 슬라이드 내용을 자세히 보시면 엔비디아 GPU 그림과 함께 CoWoS 기술을 설명하죠. GPU를 둘러싼 6개 HBM을 탑재할 수 있는 4세대 CoWoS는 3년 전인 2019년 상용화했습니다.

이 4세대 CoWoS를 사용했더니, 트랜지스터 수는 200억개에서 540억개로 늘어나고, HBM 용량이 최대 32기가바이트(GB)에서 90GB까지 증가했다고도 소개합니다. 또 CoWoS 기술 덕분에 서버 구축 비용과 전력이 각각 10분의 1, 20분의 1 씩 줄었다는 것까지 공개했습니다. 데이터 센터 안에서 서버가 차지하는 면적이 홀쭉해진 것도 감상 포인트입니다.

TSMC가 세계 최대 팹리스이자 고객사인 '엔비디아'와 3년 전 패키징 협력 결과물을 공개한 것은 '과시'의 메시지이기도 한 것 같습니다.

현재까지 라이벌 삼성전자가 선보인 가장 최신 연산장치·HBM 패키징 기술 지난해 11월 발표한 'H-큐브'입니다. TSMC 4세대 CoWoS처럼 HBM을 6개 배치할 수 있는 기술입니다. 삼성이 파운드리 사업에 늦게 시동을 건 만큼 패키징 기술 격차가 TSMC에 비해 다소 벌어진 점은 어쩔 수 없는 것 같습니다.

TSMC는 이 분야에서 가만히 있지 않고 앞서가는 모습입니다. 삼성전자가 H-큐브 스펙을 발표한 지난해, 8개 HBM를 탑재할 수 있는 5세대 CoWoS 개발 완료를 밝혔죠. 여기에는 최신 HBM인 HBM3가 활용된다고 합니다. 올 6월 세계에서 처음 HBM3를 양산해 엔비디아에 공급한다고 밝혔던 SK하이닉스가 관여돼 있을 공산이 상당히 큽니다.

또 2023년에는 12개 HBM을 탑재하는 패키징 기술을 양산할 것이라고도 선언했습니다. 이 기술 격차를, 파운드리 육성에 한창인 삼성전자가 역전할 수 있을지 지켜보는 것도 관심 포인트입니다.

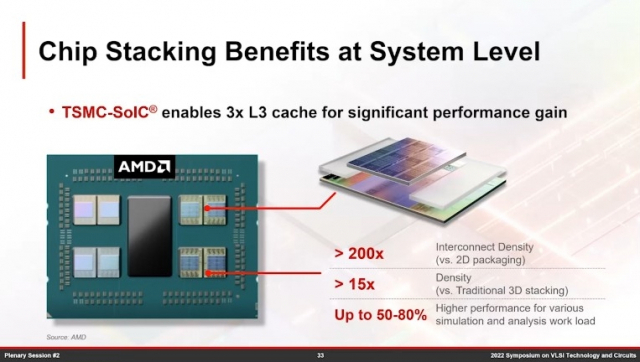

엔비디아와의 협력 외에도 TSMC는 AMD와의 최신 협력 사례도 듭니다. 기존 범프 공정을 뛰어 넘은 하이브리드 본딩(SoIC) 3D 패키징 기술로 칩을 만들었더니, 집적도는 15배 이상, 성능은 50~80% 개선했다고도 알렸습니다. 삼성전자는 아직 하이브리드 본딩을 활용한 패키징 공정 양산을 공식 발표한 적은 없습니다.

아울러 향후 이종결합 패키징 시장에서의 자신감을 장표 하나로 나타내기도 했죠. 전(前) 공정으로는 한개 칩 안에 500억개 트랜지스터를 만들어낼 수 있다면, 각종 후공정 기술로 패키징만 잘하면 6배 수준인 3000억개 트랜지스터를 집적할 수 있다고도 발표했습니다.

TSMC 패키징은 어디까지 성장할까요. 또 최근 패키징 인프라 투자, 어드밴스드 패키징 TF 조직 등을 결정한 라이벌 삼성전자는 파운드리 분야에서 빠르게 격차를 좁혀갈 수 있을까요?

지금까지 TSMC VLSI 발표 자료의 주요 포인트를 짚어봤습니다. 서두에도 언급드렸듯이 미위졔 수석부사장이 소개한 기술은 TSMC 외에도 다양한 파운드리 업체, 칩 설계 업체, 소재 업계, 학계가 주목하고 있는 기술입니다. TSMC 외에도 다양한 반도체 엔지니어들이 이 기술을 하루 빨리 먼저 구현하기 위해 곳곳에서 노력하고 있죠.

반도체가 '경제 안보' 자산이 된 지금, 우리나라도 풍부한 반도체 R&D 인프라를 구축해 전·후공정 전반에서 핵심 미래 기술 경쟁력을 확보할 수 있길 바라면서 글을 마칩니다. 가을 바람과 함께 즐거운 하루 보내세요.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com