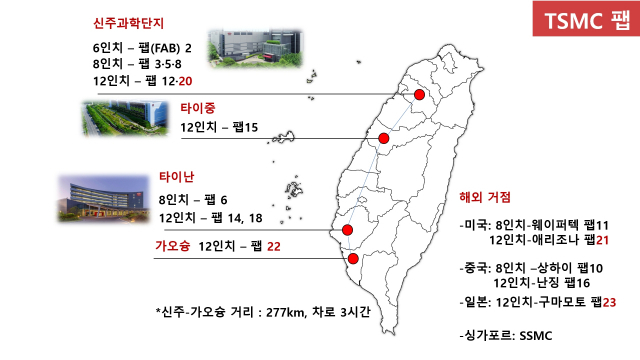

정보기술(IT) 시장에 관심 많으신 독자 여러분, 안녕하세요. 지난주 강해령의 하이엔드 테크 '대만 TSMC 팹, 어디까지 가봤니'에서는 위 그림처럼 TSMC의 전(前)공정 공장 위치와 생산 능력을 살펴봤는데요. 2탄에서는 TSMC의 후(後)공정 인프라에 대해 다뤄보려고 합니다. 반도체 후공정은 '패키징', 또는 '백엔드'라는 용어로도 익숙합니다. 요즘 반도체 업계에서 유행처럼 조명받고 있는 분야이기도 하죠. 이번 기사에서는 TSMC가 얼마나 적극적으로 이 분야에 대해 투자하는지 각종 자료를 통해 짚어보겠습니다.

이번 시리즈는 3탄도 준비해봤는데요. 다음 회에선 TSMC가 선도적인 투자로 확보한 첨단 후공정 분야 영향력 함께 최근 사업에 뛰어든 삼성전자의 현황, 국내 시스템 반도체 생태계의 모습과도 비교하면서 국가적 투자의 필요성도 체크하려 합니다. 자, 그럼 지난 1편처럼 대만 지도를 하나 펼치면서 시작해봅시다.

파운드리 TSMC, 패키징 공장만 5개

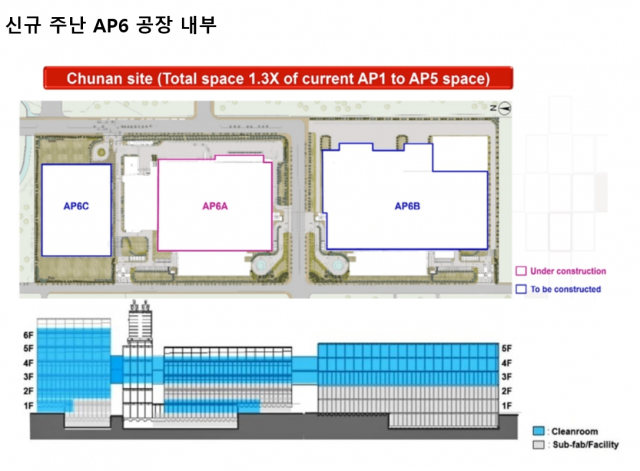

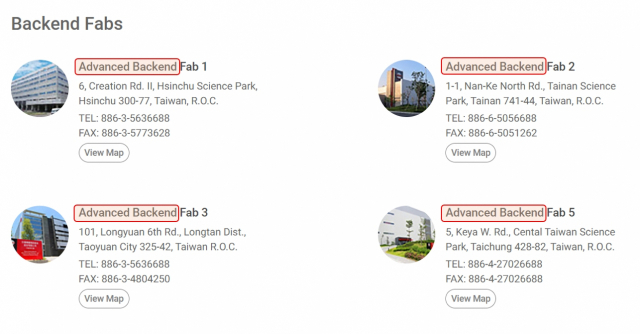

오른쪽 대만 지도에 찍힌 5개의 붉은 점. TSMC의 후공정 공장 위치를 나타냅니다. TSMC는 TSMC 본사가 있는 신주(AP1)부터 타이난(AP2), 롱탄(AP3), 타이중(AP5), 주난(AP6)까지 총 5개의 후공정 팹(공장)을 운영합니다.

이들 중에선 가장 최근인 지난해 3분기부터 가동을 시작한 AP6의 면적이 가장 큽니다. AP6는 나머지 4개 공장의 면적을 합친 것보다 1.3배나 더 큰 패키징 공장이라고 합니다. TSMC가 시간이 지날수록 패키징 분야에 공을 들이는 것은 공장 면적 확대만 보더라도 쉽게 알 수 있습니다. 지난해 초에는 대만 언론에서 TSMC가 현지 남부 자이 시에 6번째 패키징 공장 건설을 검토한다는 보도도 있었습니다.

일본에도 패키징 거점을 지었습니다. 지난해 6월 TSMC는 일본 이바라키 현에 4000억원에 가까운 예산을 투자해 패키징 연구개발센터를 열었죠. 일본 안에 있는 이비덴 등 반도체용 기판 업체와 소재 협력 연구를 적극적으로 진행할 것으로 보입니다.

TSMC가 빠르게 공장과 연구 설비를 늘려나가는 만큼 이들의 패키징 생산 능력 확대 속도는 무섭습니다. TSMC 측은 지난해 한 발표에서 2022년 패키징 생산 능력이 2018년 때보다 300% 이상 늘어날 것으로 기대한다고 밝힌 적 있을 만큼 자신감도 넘칩니다.

그럼 이곳은 무엇을 하는 곳일까. 이걸 알기 위해 우리는 TSMC의 팹 이름을 한번 뜯어볼 필요도 있습니다. TSMC는 후공정 팹 숫자 앞에 '첨단 백엔드(Advanced Backend)'라는 숫자를 붙입니다. AP1의 AP도 '어드밴스드 패키징(Advanced Packaging)'의 줄임말이죠. 왜 백엔드와 패키징 앞에 '첨단'을 붙였을까. 파운드리 업계에서는 '우린 쉬운 패키징은 하지 않겠다' 정도의 의미로 해석합니다.

TSMC 5개 공장에서 가동되는 InFO·CoWoS·SoIC

반도체 업계에서 패키징은 말 그대로 포장 작업입니다. 전공정으로 완성된 칩이 기판과 호환할 수 있도록 배선을 설치하고 소자를 고열과 오염 등에서 보호하는 막을 씌우는 일이죠.

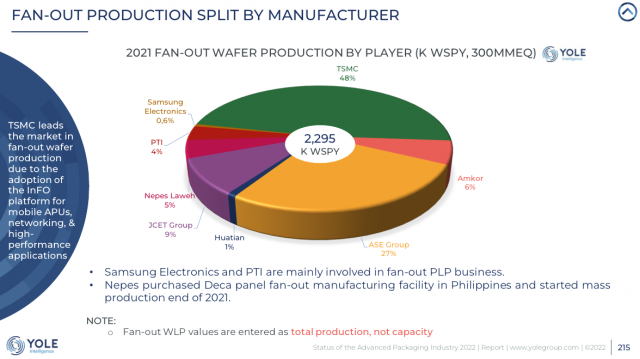

TSMC가 패키징 기술 중에서 자부심을 느끼는 분야는 고급 기술로 분류되는 '팬아웃(fan out·FO)' 웨이퍼 레벨 패키징(WLP)입니다. 이 기술로 TSMC는 패키징 업계의 초대형 스타가 됐습니다. 차근차근 용어를 뜯어봅시다.

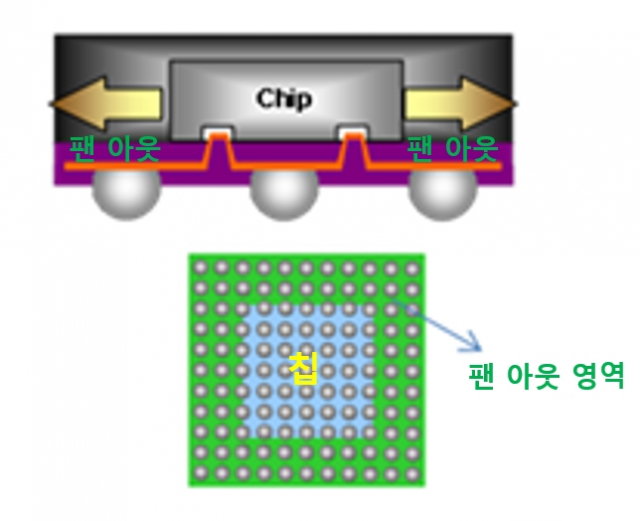

먼저 팬 아웃이라는 걸 사전에서 찾아보면 '~을 펼치다'라는 뜻입니다. 패키징에서는 ‘연결 단자’를 칩 바깥으로 펼치는 콘셉트입니다. 최근 칩 연산 기능이 발전하면서 정보 이동 통로(I/O)가 너무 많이 필요해지게 됐습니다. 이에 따라 반도체의 가장자리를 벗어난 곳까지 연결선을 펼쳐 정보 출입 최적화를 도모하는 거죠. 그림을 보시면 쉽게 이해하실 수 있습니다.

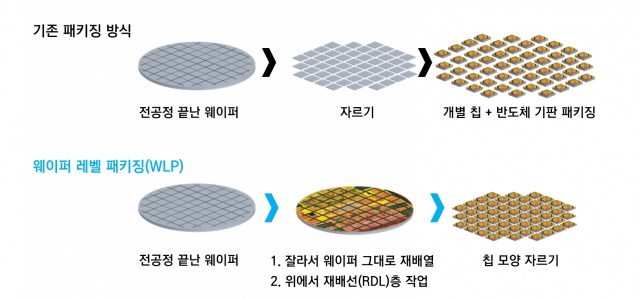

그럼 이제 웨이퍼 레벨 패키징(WLP)를 봅시다. WLP는 기존 방식처럼 칩 하나하나를 잘라서 기판을 대고 선을 연결해서 포장하지 않습니다. 칩을 가지런하게 자르되 동그란 웨이퍼의 모습 그대로 다시 배열하고, 그 위에 한번에 재배선층을 쫙 깔아서 작업을 진행하는 걸 말합니다.

WLP는 장점이 정말 많습니다. 통상 쓰는 플립칩(FC)-볼그리드어레이(BGA), 플립칩(FC)-칩사이즈패키징(CSP) 같은 반도체용 기판을 쓰지 않아서 두께가 훨씬 얇아지고요. 배선이 짧아지니까 전기적 특성도 향상합니다. 또 일단 칩을 가지런히 재정비한 다음 배선 작업을 하는 방식, 일명 ‘칩 퍼스트’ 방식을 쓰니까요. 원래 방법과 비교하면 추가 공정 없이도 서로 다른 성격의 칩들과 수평 결합에 상당히 유리합니다. 유즘 유행하는 이종(異種)결합, 즉 2.5D 또는 헤테로지니어스 패키징에도 잘 대응할 수 있죠.

TSMC가 FOWLP 공정을 구현하는 것이 말처럼 쉽지는 않았습니다. 수율을 올리고 단점을 극복하기 위한 대단위 연구 개발이 필요했고 시설 투자도 많이 해야 했기 때문이죠.

TSMC는 2016년 이 FOWLP 분야에 과감하게 투자를 해서 큰 성공을 거둡니다. 특히 ‘경박단소’ 칩을 스마트폰에 넣고 싶었던 애플의 마음을 홀랑 빼앗아갔습니다. 이것은 TSMC가 당시 삼성전자와의 애플 칩 파운드리 경쟁에서 승리를 거두고 지금까지 FOWLP 시장 리더십을 가지게 된 강력한 무기가 됐습니다.

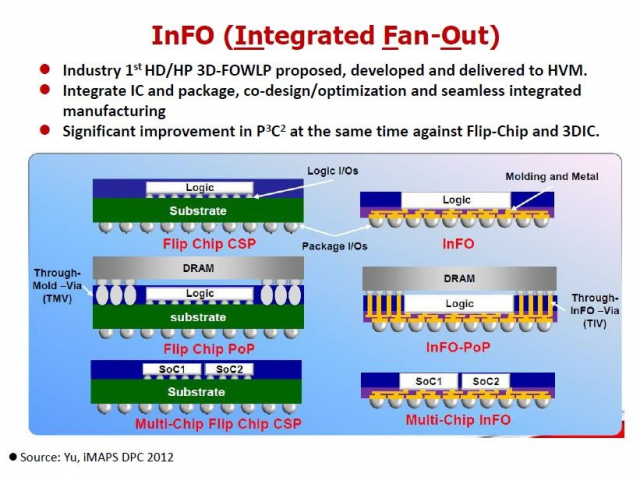

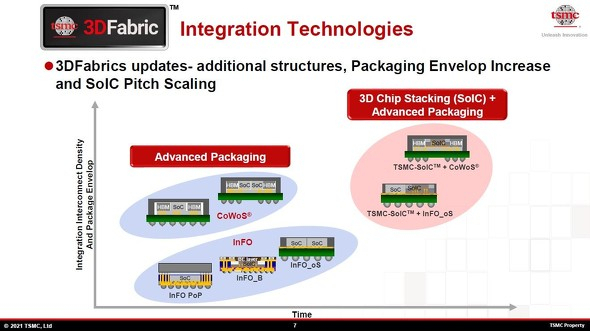

여기서 끝이 아닙니다. 반도체 업계에서는 한 칩 안에서 회로 폭 줄이기가 너무 힘들어지니까 시간이 흐를수록 2.5D·3D 패키징, 즉 이종결합에 눈을 돌리기 시작했는데요. TSMC는 이 기회를 놓치지 않고 세 가지 서비스로 고객사들에 다가갑니다. FOWLP 기반 기술인 '통합 팬아웃(InFO·Integrated Fan Out)' 기술을 더욱 업그레이드해서 각종 칩들을 하나로 결합하는 패키징 솔루션을 제공하고요.

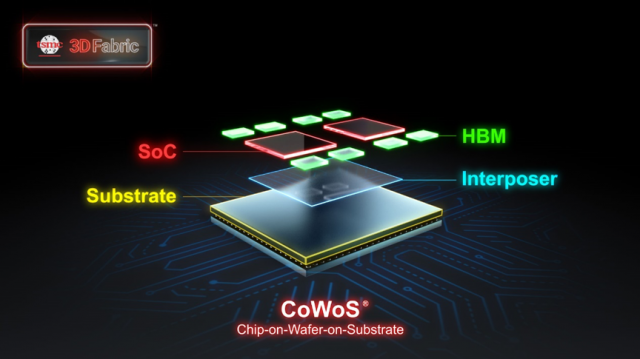

'CoWoS'라는 브랜드도 활발히 마케팅 중입니다. CoWoS에서는 반도체용 대면적 기판(BGA)을 쓰는데요. 칩과 기판 간 중재자 역할을 하는 실리콘(Si) 인터포저라는 소재를 덧대서 전기 특성을 높였기 때문에 '칩온웨이퍼온서브스트레이트'라는 용어를 씁니다. 서버·인공지능(AI)에 쓰이는 고사양 칩을 위한 기술이고요. 여러 개의 칩과 고대역폭메모리(HBM) 등을 원하는 대로 배열할 수 있습니다. 이 기판에 얹을 수 있는 HBM 수는 계속 늘어나는 추세입니다. 미국 엔비디아가 이 서비스를 아주 잘 활용하고 있습니다.

또 요즘은 3D 패키징 분야 소개에도 진심입니다. 일명 '하이브리드 본딩(SoIC)'이라고 해서 칩과 칩을 쌓는 게 아니라 아예 '포개어버리는' 기술인데요. 미국 AMD와 협력 사례를 발표하는 등 매출 확보에 주력하고 있습니다. 마치 정말 실력 좋은 주택 리모델링 시공 회사 같기도 합니다. “원하는 붙박이장, 벽지, 단창·이중창 샤시 등 일단 말씀만 하시라, 다 구현해드린다.” 이런 식인거죠.

마무리하면 TSMC는 위에서 소개드린 기술들을 5개 패키징 공장에서 운영하고 있습니다. TSMC는 이 곳이 차세대 반도체 시장의 승부처라고 생각하고 주도권을 잡고 싶어합니다. 2016년 FOWLP 성공으로 대스타가 된 뒤 패키징 투자에 진심인데요. 과연 TSMC의 패키징 분야 영향력은 어떤지, 삼성전자 등 우리나라 패키징 기술 어디까지 왔는지 등은 이어지는 3편에서 살펴보려고 합니다. 예고편 격으로 아래 장표 하나 보여드리면서 기사 마무리합니다. 감사합니다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com