삼성전자가 차세대 메모리로 불리는 3차원(D) D램 개발에 속도를 내고 있다. 세계에서 3D D램 제조 기술을 가장 먼저 확보해 독보적 D램 1위의 위상을 이어나가겠다는 전략으로 읽힌다.

19일 업계에 따르면 삼성전자 차세대공정개발팀은 지난달 일본에서 열린 세계 최대 반도체 학회인 ‘2023 VLSI 심포지움’에 참가해 3D D램 연구 성과가 담긴 논문을 발표했다. 삼성전자는 이 논문에서 ‘수직 적층(VS·Vertically Stacked)-D램’이라는 명칭과 함께 3D D램을 정의했다.

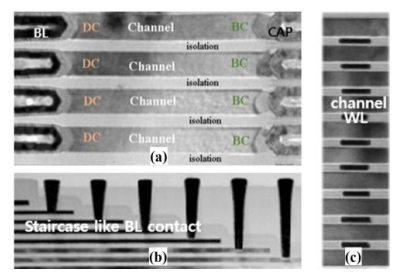

회사는 이 논문에 여러 3D D램 공정 실험에서 얻어낸 현미경 사진을 함께 실었다. 이들은 전자가 흐르는 통로인 채널 형성을 위해 실리콘(Si)·실리콘 저마늄(SiGe) 층을 반복해 쌓은 모습, 3D D램 콘셉트대로 기억 장치들을 쌓아 올린 모습을 촬영한 사진을 상세히 공개했다. 삼성전자 외에도 SK하이닉스, 미국 마이크론 테크놀로지, 중국 메모리 업체들이 3D D램의 가능성과 설계도 등을 대중에 언급한 적은 있으나 이번처럼 상세한 실험 이미지를 제시한 것은 상당히 이례적이다.

또한 삼성전자 측은 저장 장치와 주변 회로부를 따로 제작해 이어 붙이는 패키징 기술을 3D D램에 적용할 수 있다고도 설명했다. 이 기술은 메모리 업계에서는 낸드플래시 업체들이 적용한 사례는 있지만 D램에서는 적용된 적이 없다. 삼성전자 측은 각종 실험 결과에 대해 “칩 결합·적층 기술이 10㎚(나노미터·10억분의 1m) 이하 D램 시대의 한계를 극복할 돌파구가 될 것”이라고 자평했다.

삼성전자가 도전하고 있는 3D D램은 칩 안에 있는 기억 소자를 아파트처럼 세로로 쌓는 차세대 D램이다. 현재의 D램은 평평한 면에 수백 억 개의 기억 소자를 배열한다. 만약 트랜지스터를 수직으로 적층한다면 회로 축소 부담을 덜 수 있을 뿐만 아니라 용량을 폭발적으로 높일 수 있다고 업계는 분석하고 있다.

다만 기술 구현이 어렵고 공정이 복잡해서 아직 원천 기술을 확보한 업체는 나타나지 않았다. 업계 관계자는 “이 기술을 먼저 확보할 경우 D램 패러다임을 통째로 바꿀 수 있다”며 “미국의 강력한 반도체 제재를 받는 중국 업체들도 3D D램 특허 확보에 주력하고 있다”고 설명했다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com