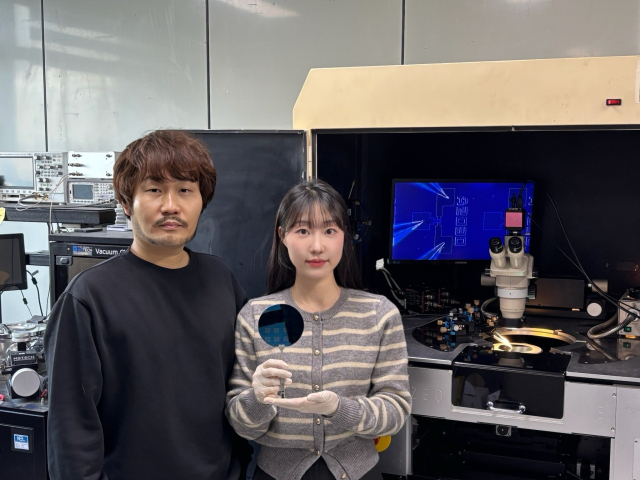

박태주 한양대 교수 연구팀이 세계 최초로 2차원 전자기체 채널을 적층한 ‘3진법’ 논리 소자(트랜지스터)를 개발했다고 14일 밝혔다. 인공지능(AI) 분야에서 폭증하고 있는 데이터를 현존하는 반도체 칩보다 빠르고 효율적으로 처리할 수 있는 소자로 기대를 모으고 있다.

박교수 연구팀의 연구 성과는 지난해 12월 세계적인 학술지인 ‘어드밴스드 사이언스’의 표지 논문으로 게재됐다.

트랜지스터는 반도체 칩 안에서 전기 신호에 따라 꺼지거나 켜지는 스위치 역할을 한다. 이 소자가 각종 정보를 연산하는데, 현재 대부분의 반도체 칩은 0과 1, 즉 2진법 논리에 기반한다.

그러나 최근 AI 발전과 함께 처리해야 할 정보가 폭발적으로 증가하는 것이 문제로 떠올랐다. IT 업계는 동일한 칩 면적에 최대한 많은 2진법 트랜지스터를 넣어서 가능한 많은 정보를 연산하려는 시도를 했다. 그러나 이 기술로는 연산량을 감당하지 못하는 상황에 이르렀다.

3진법 트랜지스터는 이러한 한계를 극복한다. 3진법은 기존 2진법에서 벗어나 0, 1, 2의 세 가지 상태를 가질 수 있는 스위칭 소자이다. 동일한 연산 수행을 위해 요구되는 소자의 개수가 기존 2진법 소자에 비해 크게 감소해 같은 면적 안에 더욱 많은 소자를 배치할 수 있다. 공정 부담을 줄이면서 성능 개선, 소비 전력까지 크게 낮출 수 있는 방법인 셈이다.

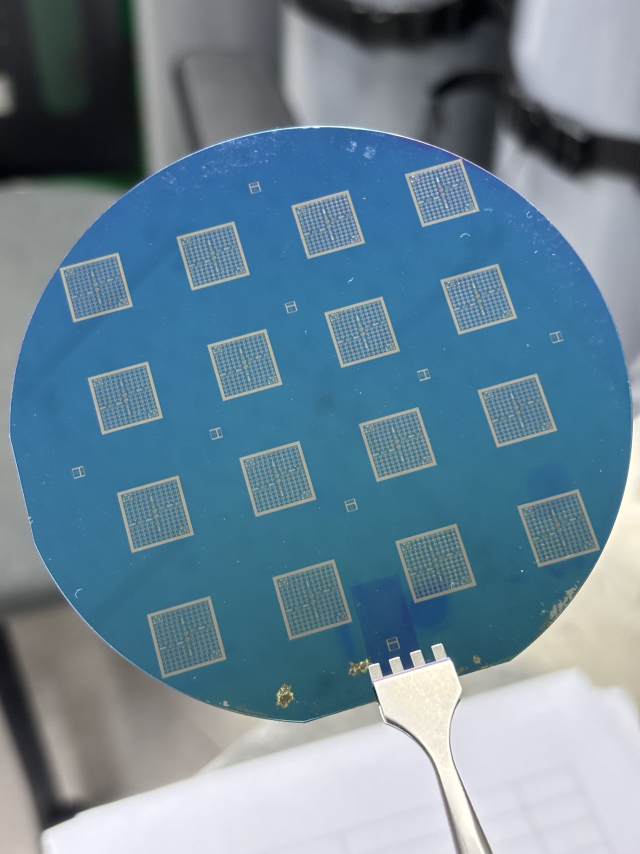

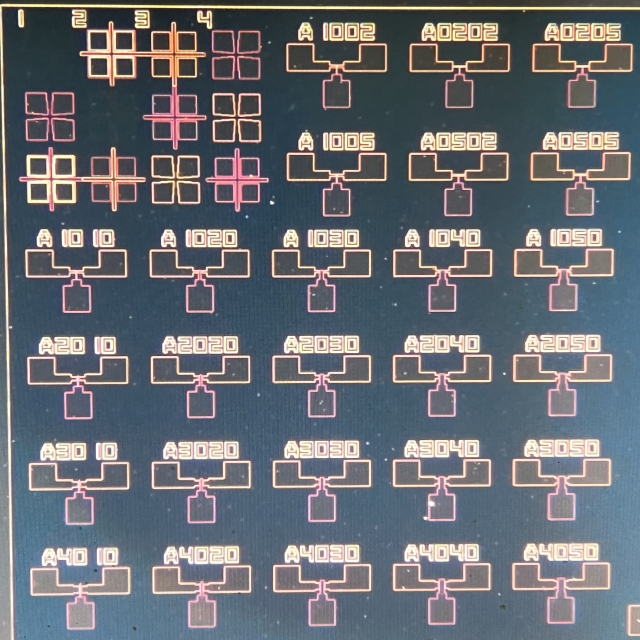

박 교수 연구팀은 현존하는 반도체 양산 공정으로도 이 소자를 구현할 수 있다고 강조했다. 연구팀은 차세대 공정 기술로 꼽히는 원자층 증착 공정(ALD)을 적극 활용했다. ALD 공정에서 발생하는 표면 화학 반응을 응용해 약 5 나노미터 (㎚·10억 분의 1m) 두께의 산화물 이종접합 (Al2O3·ZnO) 계면에 고농도의 2차원 전자기체 채널을 형성했다. 이 2차원 전자기체 채널을 2단으로 적층해 3진법 트랜지스터를 만들었다.

박 교수는 “이번 연구 결과는 2차원 전자기체 채널 적층 기술을 기반으로 하는 3진법 논리 소자를 세계 최초로 구현했다는 점에서 의미가 크다”며 “현행 양산 공정인 ALD 공정을 활용해 차세대 초저전력 반도체 소자의 가능성을 제시했다는 점이 고무적”이라고 설명했다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >