한국과 미국 공동 연구를 통해 차세대 인공지능(AI) 반도체로 주목받는 프로세싱인메모리(PIM)의 성능을 크게 높이는 기술이 개발됐다. PIM의 고질적 한계를 극복함으로써 상용화를 앞당기는 데 기여할 것으로 기대된다.

한국과학기술원(KAIST)은 김동준 전기및전자공학부 교수 연구팀이 미국 노스이스턴대와 봇턴대, 스페인 무르시아대와의 공동 연구를 통해 PIM의 통신 속도를 크게 높이는 ‘PIM 반도체 간 집합 통신에 특화한 인터커넥션 네트워크 아키텍처’를 개발했다고 20일 밝혔다. 연구성과는 다음 달 컴퓨터 구조 분야 국제 학술대회 ‘HPCA 2025’에서 발표될 예정이다.

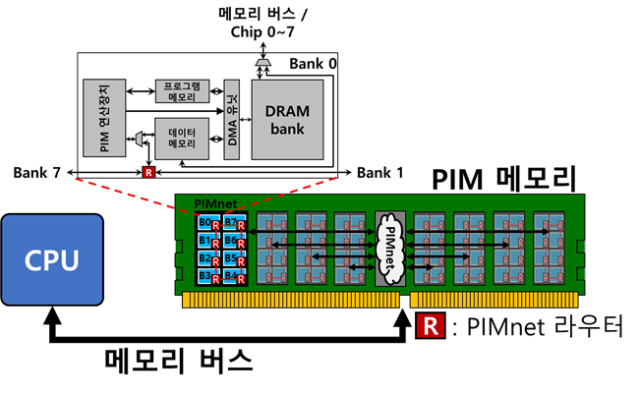

PIM은 메모리 안에 연산 장치를 넣은 차세대 메모리다. 그래픽처리장치(GPU)와 고대역폭메모리(HBM)에 이은 차세대 AI반도체로 주목받으며 삼성전자 등도 기술을 개발 중이다. 다만 PIM은 데이터 연산과정에서 외부 중앙처리장치(CPU)와 신호를 주고받아야 하는 구조적 한계가 있다. CPU와 통신하는 과정에서 데이터 병목현상이 발생해 성능을 높이는 데 한계가 있는 것이다.

연구팀은 PIM과 CPU 간 통신을 최소화하기 위해 인터커넥션 네트워크를 도입했다. PIM의 연산 장치들이 CPU를 통하지 않고도 서로 직접적으로 통신하는 기술이다. 이를 통해 PIM의 통신 속도를 기존 대비 11배 향상시켰다고 연구팀은 설명했다.

김 교수는 “데이터 이동을 줄이는 것은 PIM을 포함한 모든 시스템반도체에서 핵심적인 요소”라며 “PIM은 성능과 효율성을 높일 수 있지만 연산장치 간 데이터 이동으로 인해 성능 확장성에 제약이 될 수 있어 응용분야가 제한적”이라고 설명했다. 그러면서 “PIM 인터커넥션 네트워크가 이에 대한 해법이 될 수 있다”고 말했다. 그는 최근 미국 전기전자공학회(IEEE) 컴퓨터 아키텍처 분야에서 한국 최초로 펠로(석학회원)으로 선임됐다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

sookim@sedaily.com

sookim@sedaily.com