정보기술(IT) 시장에 관심 많으신 독자 여러분, 안녕하세요. 22일 [강해령의 하이엔드 테크]에서는 제 2의 HBM으로 불리는 '소캠(SOCAMM)'에 대해 다뤘습니다.

기사 출고 이후 독자님들께서 많은 질문을 주셨습니다. 특히 소캠 모듈에 장착돼 있는 한 개의 LPDDR D램 칩 속에 다이(Die)들이 어떤 형태로 결합돼 있는지에 대한 피드백을 주셨습니다.

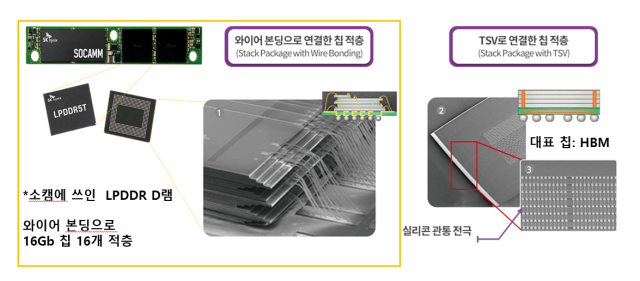

16개의 다이가 '와이어 본딩'으로 묶여있는지, 고대역폭메모리(HBM) 이후 화두가 되고 있는 실리콘관통전극(TSV)이 활용된 것인지에 대한 내용이었는데요. 이 물음에 대한 답을 찾아가 보려고 합니다. 지금부터 취재한 내용을 말씀드리겠습니다.

소캠용 LPDDR도 와이어 본딩으로 만듭니다

소캠의 콘셉트에 대해 간단히 요약드리겠습니다. 소캠은 저전력 D램(LPDDR D램)으로 만든 메모리 모듈입니다. LPDDR D램은 스마트폰·PC에 굉장히 많이 쓰입니다. 전력이 화두인 서버에서도 탑재되는 추세고요. LPDDR에서 LP는 Low Power의 줄임말입니다. 일반적인 DDR D램보다 전력을 덜 소비한다는 특징이 있습니다.

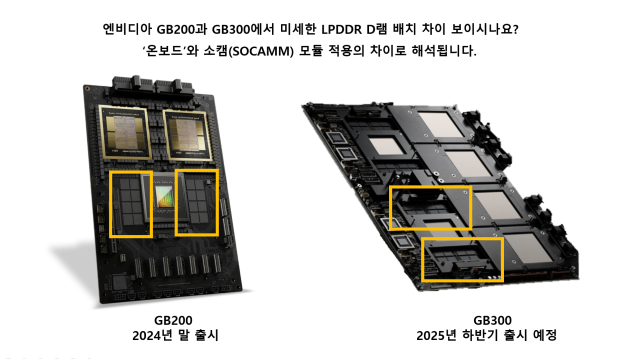

LPDDR D램은 모듈 형태가 많지 않았습니다. IT 기기에 칩을 곧바로 갖다 붙이는 '온보드' 방식이 대세였기 때문입니다. 특히 노트북 PC 쪽에서 더 그랬습니다. 요즘 와서 LPCAMM이라는 모듈이 뜨기 시작했지만, 서버 쪽에서도 대부분 온보드 방식을 활용해왔습니다.

하지만 이 방식은 비용이 많이 들고, 차세대 고용량·고효율 D램이 등장할 경우라면 보드를 아예 다 뜯어서 교체해야하는 배보다 배꼽이 더 큰 치명적 단점이 있습니다.

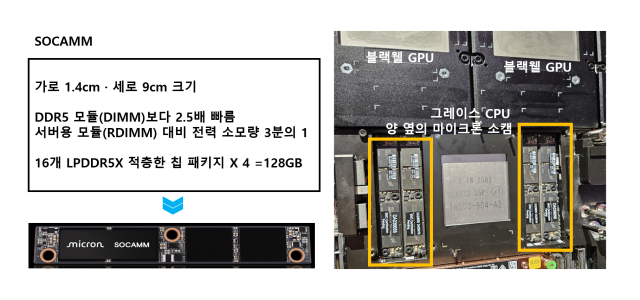

이 문제를 해결하는 게 바로 소캠입니다. Small Outline Compression Attached Memory Module. 조그맣게 생긴 녀석이 탈부착까지 가능하다는 모듈입니다. 엔비디아가 독자 추진하는 표준이며, LPCAMM보다는 크기가 더 작으면서 정보 이동 통로 수가 많다는 특징이 있습니다.

엔비디아는 올 하반기 양산할 AI 서버 GB300부터 이 모듈을 활용한다고 합니다. 소캠의 경우 서버를 제어하는 그레이스 CPU 양 옆으로 4개의 모듈이 붙는데요.

모듈을 좀 더 자세히 보면요. 한 기판 위에는 4개의 LPDDR D램이 붙습니다. 각 LPDDR D램 속에는 16개의 다이가 아파트처럼 적층돼 있습니다. 16Gb D램을 16층 쌓아서 32GB 용량의 칩을 구현하죠. 이 지점부터 독자님들이 궁금증을 가지셨습니다. 메모리 회사들은 이 칩들을 어떤 방식으로 쌓았을까.

그간 삼성전자(005930)·SK하이닉스(000660)에서는 와이어 본딩이라는 패키징 방식으로 LPDDR 다이를 결합한 것으로 알려졌습니다.

소캠 분야의 ‘다크 호스’인 미국 마이크론 테크놀로지도 관심이 갈 수밖에 없습니다. 마이크론은 지난주 미국에서 열렸던 엔비디아 연례 행사인 GTC 2025에서 소캠이 GB300 보드와 어떻게 결합하는지를 실물로 보여주기도 했었죠. 현재까지 소캠 분야에서 엔비디아와의 협력이 가장 진전돼 있는 것으로도 알려졌습니다.

마이크론도 우리나라 회사들과 마찬가지로 와이어 본딩을 택했습니다. 최근 저는 메일을 통해 마이크론에 "경쟁사들이 소캠용으로 쓰이는 16단 LPDDR D램 결합을 위해 와이어 본딩을 쓴다. 마이크론의 현황은 어떤가"에 대해 문의했는데요. 회사 측에서는 "국제반도체표준협의기구(JEDEC)에서 소캠에 대한 표준이 공식적으로 정해지지 않았지만, 마이크론 역시 소캠용 16층 LPDDR D램을 연결하기 위해 와이어 본딩을 활용한다"는 답변을 보내왔습니다.

사실 LPDDR D램 업계에서 다이 적층과 와이어 본딩은 새로운 이슈가 아닙니다.

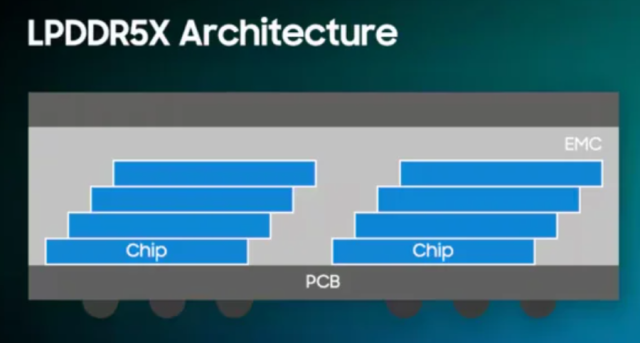

일례로 지난해 8월 삼성전자가 낸 보도 자료를 보면요. 업계 최소 두께인 0.65㎜의 LPDDR5X D램을 양산했다는 소식이 있습니다. 12나노급 LPDDR D램을 4단으로 쌓았고, 향후 8단 구조로 32GB 칩을 만들겠다는 내용을 이 자료에서 전했습니다. HBM만이 아니라 단일 D램을 여러 층으로 쌓아 양산하는 건 이미 수년 전부터 수차례 적용됐다는 이야기입니다.

이 때 적층을 하면서 와이어 본딩을 활용했을 가능성이 큽니다. 와이어 본딩은 말 그대로 배선을 칩 가장자리에 붙이는 공정인데요. 각 D램 다이를 차곡차곡 쌓은 뒤에, 칩들이 기억하고 있는 정보들이 바깥으로 이동할 수 있도록 하는 일종의 '고속도로' 선을 여러 개 연결한 것입니다.

HBM이 뜨면서 개별 다이 안에 수직 배선 구멍을 뚫어서 연결하는 TSV가 훨씬 힙해보일 수 있지만 와이어 본딩의 경험치와 기술력·성능 역시 상당합니다.

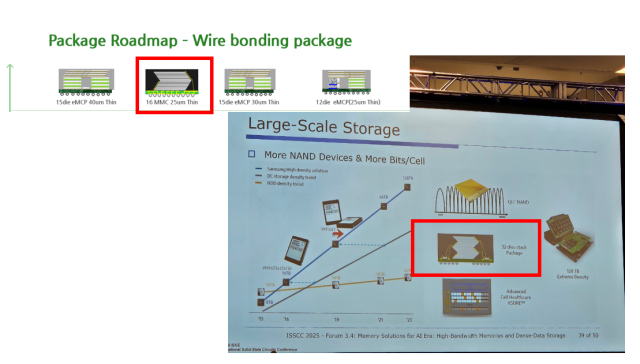

업계에는 4단·8단 뿐만 아니라 메모리 고적층 패키징 역시 와이어 본딩으로 해결할 수 있는 기술을 도입하고 있습니다. 예컨대 고용량 낸드 플래시를 만들 때 16단을 적층해 와이어 본딩하는 기술이 이미 개발돼 있다고 합니다.

심지어 삼성전자는 최근 한 기술학회에서 낸드플래시 다이를 32단으로 쌓아서 와이어 본딩으로 연결하는 기술을 구현하겠다는 아이디어까지 내놓았는데요. 이런 측면에서 볼 때 D램 분야에서도 LPDDR을 16단으로 와이어 본딩하는 것은 구현은 쉽지 않지만 어쨌든 할 만한 기술이라는 해석이 나옵니다.

그럼 이제 또 한가지. LPDDR, 특히 서버에 들어가는 LPDDR D램은 데이터 양이 폭증할 것 같은데 왜 TSV를 도입하지 않는가. 업계에서는 '굳이…?'라는 얘기가 나옵니다.

사실 LPDDR을 만들 때 TSV를 활용한다면 할 수는 있습니다. 기사 초반에 말씀드렸듯이 LPDDR D램의 핵심은 LP, 즉 저전력입니다. 와이어 본딩으로 배선을 연결했을 때보다 TSV를 활용하면 오히려 데이터 전송 대비한 전력 소모량이 개선될 수도 있습니다. 정보 출입구(I/O)와 배선 사이의 길이가 획기적으로 짧아지다 보니 한 배선마다의 전성비가 좋아져 LPDDR의 ‘저전력’ 특성이 더욱 좋아질 수 있다는 이야기죠.

그럼에도 도입하지 않는 이유는 우리가 ‘통상 집 앞 마트 갈 때 쓰려고 페라리 슈퍼카를 구입하는 선택을 하는가?’를 생각하는 것과 비슷한 문제입니다.

LPDDR에 TSV를 도입한다는 의사결정이 내려지는 순간 반도체 엔지니어들은 섬뜩한 두통을 겪게 될 것 같습니다. 우선 LPDDR의 구조를 대폭으로 바꿔야 합니다. TSV는 칩 중간에 배선 구멍을 뚫는 거라서 다이 크기 확대는 불가피하죠. 공정도 완전히 새롭게 변화해야 합니다.

칩의 원가 측면에서 봐도 그렇습니다. 제조업에 종사하는 사람들은 언제나 제조 원가를 고민해야 합니다. 와이어 본딩은 TSV와 비교했을 때 원숙한 공정이죠. 값이 저렴하면서 상대적으로 공정 난도가 낮고 단계가 적어 수율도 훨씬 좋고, 기존 LPDDR D램 제조 인프라를 활용해도 되는 데다 성능도 좋은데 굳이 새로운 것이 필요한가에 대한 견해도 있습니다.

또한 이미 엔비디아나 AI 서버 회사들은 자신들이 필요한 메모리를 찾아 적재적소에 쓰고 있는데, 굳이 LPDDR 패키징 방식을 바꾸겠느냐는 의견도 있습니다. 엔비디아 서버만 놓고 볼까요. 폭발적인 데이터를 연산해야 하는 블랙웰 같은 GPU 주변에는 HBM을, 서버 전반을 제어하는 그레이스 CPU 주변에는 상대적으로 정보처리 스펙이 HBM에 비해 덜하지만 전력 절감이 뛰어난 LPDDR D램을 배치하면서도 서버 AI 성능을 극대화했습니다.

물론 엔비디아가 앞으로 그레이스에 이은 후속 CPU 모델인 '베라'까지 상용화할 시점엔 데이터 전송 능력이 더 업그레이드된 메모리가 필요할 겁니다. 하지만 CPU의 역할과 서버의 원가 등 다양한 문제를 따져봤을 때, 이들이 앞으로도 굳이 ‘유사 HBM’스러운 오버스펙의 TSV LPDDR D램을 쓰겠느냐는 분석이 지배적입니다.

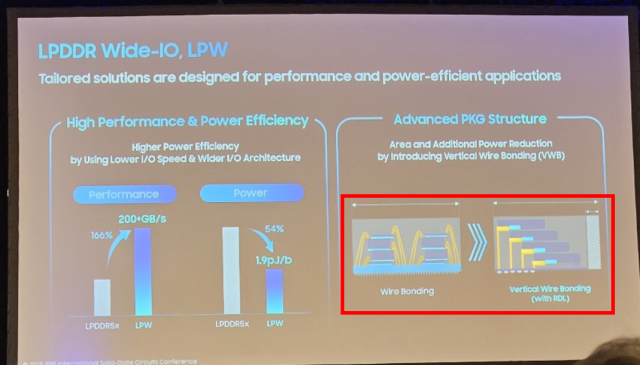

또 하나, 최근 삼성전자나 SK하이닉스의 자료들을 보면 LPDDR D램의 발전 형태로 TSV보다는 와이어 본딩을 조금 더 발전시킨 버티컬 와이어본딩(VWB)·버티컬 팬아웃(VFO) 등을 고려하고 있습니다. LPDDR D램의 근본적인 구조를 건드리는 것이 아닌 배선을 꼿꼿하고 더 멋지게 배치해보자는, 일종의 ‘포스트 와이어본딩’ 같은 아이디어입니다. 모바일 D램을 서버용인 소캠에서 그대로 활용하는 만큼, 이 공정 역시 향후 소캠 제조에 쓰일 가능성이 있습니다.

소캠의 출현으로 의외의 공정이 조명을 받는 점이 굉장히 흥미로운데요. 기존 패키징의 힘이 여전하고, '짬'에서 나오는 기술이 업계에서 여전히 지대한 영향을 미치고 있다는 점이 포인트같습니다. 모든 적층 D램이 HBM처럼 만들어지는 것으로 접근하지만 않으면 소캠 같은 신흥 메모리를 더욱 깊고 재밌게 들여다볼 수 있을 것 같습니다. 오늘은 여기까지입니다. 긴 글 읽어주셔서 감사합니다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com