2021년. 정말 '다사다낸'했죠? 저도 반도체 관련 기사를 쓰면서 독자분들께 낸드플래시 이슈 참 많이 전해드린 것 같습니다.

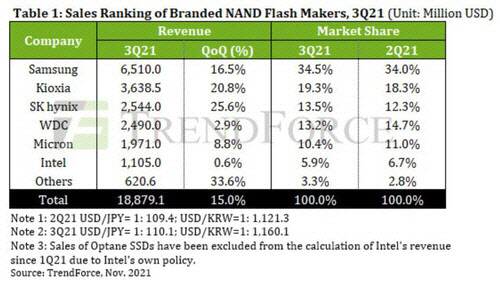

낸드 업계는 정말 숨 가쁘게 돌아가고 있습니다. 낸드 업계 1위 삼성전자는 7세대 176단 낸드플래시 양산을 위해 새로운 반도체 팹인 평택 3공장 라인을 내년에 본격 가동할 예정이고요.

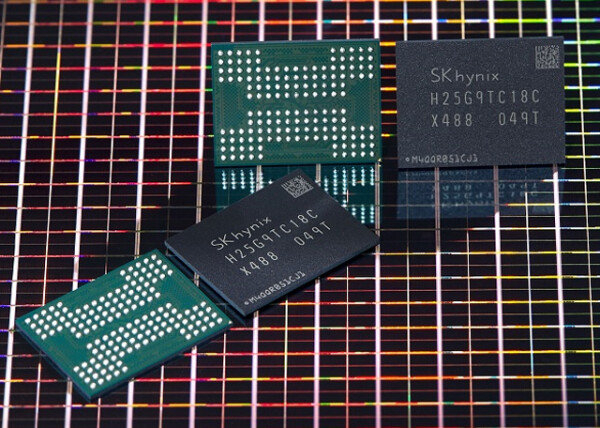

SK하이닉스도 지난해 10월 공식 발표한 인텔 낸드사업부 인수합병(M&A)에 속도를 붙이게 됐습니다. 중국 당국이 지연하던 반독점 심사 승인을 지난 22일에 끝냈으니 내년부터 차근차근, 그러나 적극적으로 자본 양수 작업에 돌입하겠네요.

미국 마이크론 테크놀로지도 매섭습니다. 올해 낸드 업계 선두권인 우리 업체들보다 먼저 176단 3D 낸드플래시 양산을 발표하며 기술력을 바짝 끌어올리고 있죠. 양쯔메모리테크놀로지(YMTC) 등 중국 낸드 후발업체의 반도체 굴기 움직임 역시 여전합니다.

내년 IT 시장에서는 낸드 수요가 크게 올라갈 것으로 보입니다. 이에 따라 기술 고도화에 대응하는 낸드 '쌓기' 경쟁도 더욱 치열하게 전개될 것으로 보입니다. 우리는 내년 200단 이상 낸드를 볼 수 있을까요?

그런데 여러분. 평소 반도체 기사를 읽던 중 낸드 플래시 기술에 대한 호기심 없으셨나요. 낸드는 높이 쌓는 게 경쟁력이라고 하던데, 무엇을·어떻게·왜 쌓는 것인지, 또 어떻게 정보를 저장하는지 한번쯤 궁금하신 적 있지 않나요? 오늘은 앞으로도 풍성할 낸드 이슈에 대비해 기사에 자주 등장하는 낸드플래시 용어를 짚어보려고 합니다.

오늘 이야기에 모든 낸드 동작 원리를 담을 수는 없습니다. 그러나 앞으로 낸드 기사 읽으실 때 도움이 될만한 핵심 3D 낸드 핵심 동작 콘셉트와 용어 위주로 취재하고 정리했습니다.

차세대 낸드 시장 전망에 대해서도 준비해봤는데요. 김기남 삼성전자 종합기술원 회장이 최근 'IEDM 2021'이라는 학회에서 보여준 낸드플래시 시장 기술 로드맵을 보면서 관전 포인트를 짚어보려 합니다.

기사 스크롤 압박이 심합니다. 이번 특집은 두 편으로 나눴습니다. ‘1탄’에는 낸드 동작 원리와 3D 낸드 구성, 차세대 낸드 기술 전망은 ‘2탄’에 준비했습니다. 바로 뒤에 링크 걸어드리겠습니다. 분량이 길지만 엑기스 추출을 위해 노력했습니다. 일단 우리 천천히, 3D 낸드 동작 원리부터 살펴봅시다.

◇낸드플래시 '셀' 동작 원리부터 뜯어봅시다

낸드(NAND) 플래시는 '비휘발성 메모리'입니다. 휘발성인 D램과는 달리, 전원이 꺼져도 정보를 기억하는 저장 장치라는 얘긴데요. 여러분의 USB, 솔리드스테이트드라이브(SSD) 속에는 이 칩이 탑재돼 있죠. 그럼 낸드플래시가 어떻게 데이터를 저장하는지 살펴봅시다.

낸드플래시에서 정보를 저장하는 최소 단위를 '셀(Cell)'이라고 합니다. 정보가 들어가는 방이라고 보시면 쉽습니다.

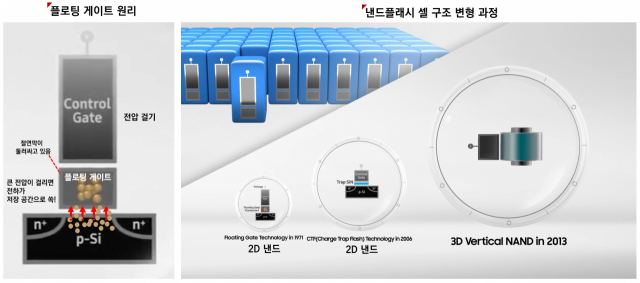

낸드 셀은 그림과 같이 크게 △전압을 거는 컨트롤 게이트 △전기 알갱이를 저장하는 플로팅 게이트 등으로 나뉩니다.

낸드플래시와 다른 반도체의 가장 큰 차이점은 바로 '플로팅 게이트'가 있다는 겁니다. 플로팅 게이트는 전기가 통하지 않는 '절연체' 막으로 둘러싸인, 전하를 꽉 잡아놓고 저장하는 공간입니다. 절연체가 저장 공간을 감싸고 있기 때문에, 전원이 꺼지더라도 전하들이 못 빠져 나가서 정보가 사라지지 않는 거죠.

간략한 낸드 작동 원리는 이렇습니다.

① 컨트롤 게이트에 큰 (+) 전압을 걸면

② (-) 전하가 게이트 밑으로 와글와글 모이게 되고요. 워낙 큰 전압이다 보니 알갱이들은 플로팅 게이트를 둘러싼 절연체(부도체)까지 뚫고 쏙 들어갑니다.

③ 플로팅 게이트 속 전하 양에 따라 디지털 신호가 저장됩니다. 예를 들어 전하가 많이 저장되면 0, 저장돼 있지 않으면 1로 저장하는 식으로 약속을 하는 거죠. 전압 크기로 이 전하 양을 조절하는데, 이 전압 값을 ‘문턱 전압’이라고 합니다.

이렇게 0 또는 1. 셀 속 무수한 플로팅 게이트가 이 디지털 신호를 저장하면서 데이터를 기억합니다.

◇그럼 3D 낸드플래시 속을 조금 더 자세히 들여다볼까요

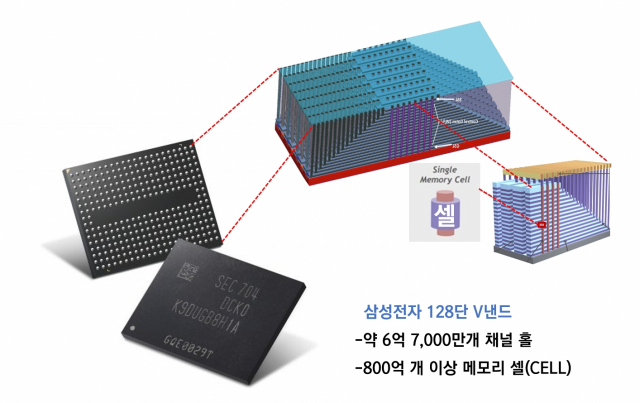

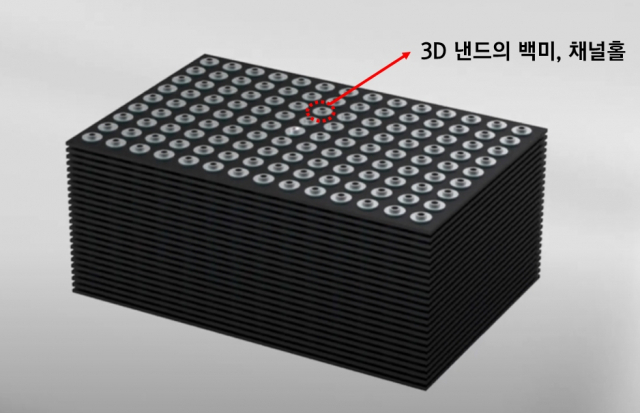

무수한 셀이라. 그럼 손톱만한 3D 낸드 칩 속에 셀은 몇 개가 있는 것인지 가늠해볼까요. 최근 나온 삼성전자 공식 자료로 살펴봅시다.

2019년 삼성전자가 공개한 6세대 V낸드, 128단 낸드플래시 자료 기준입니다. 공개된 스펙을 하나하나 뜯어보면서 셀 개수를 파악하고, 각종 용어를 살펴볼게요.

① 256기가비트(Gb) 용량

② 한 셀 당 3개 디지털 신호(0 또는 1)를 저장할 수 있는 트리플레벨셀(TLC)

③ 128단

자, 우리는 ①과 ②를 힌트 삼아 이 낸드 칩에 몇 개의 셀이 들어있는지 알 수 있습니다.

우선 256Gb라는 것은 디지털 신호(0 또는 1)를 저장할 수 있는 용량입니다. 기가(G)는 2의 30승, 약 10억입니다. 그러니까 256x10억, 총 2560억개 0 또는 1을 기억할 수 있는 능력이 이 낸드플래시에 있다는 이야기입니다.

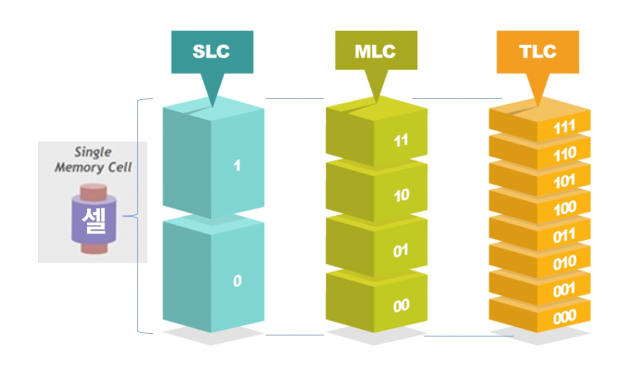

그 다음 주목해야 할 용어가 ②번, TLC입니다. 한 개 셀 안에 몇 개 0 또는 1을 집어넣을 수 있는지를 나타냅니다. TLC는 '트리플 레벨 셀', 즉 한 셀에 3개의 디지털 신호를 집어넣어 정보를 저장할 수 있다는 뜻입니다.

'000' '001' '010' '011' '100' '101' '110' '111'. 총 8 가지(2의 3승) 경우의 수가 셀 안에서 일어나겠네요. 전기 알갱이 양을 총 8 단계로 나눠 조절하면서 이 기술을 구현합니다.

참고로 한 개 셀에 1개 숫자만 넣수 있다면 SLC(싱글레벨셀), 2개 숫자는 MLC(멀티레벨셀), 3개 숫자는 TLC, 4개 숫자는 QLC(쿼드레벨셀)라고 부릅니다.

동일한 셀 면적에 더 많은 양의 숫자를 저장할 수 있는 것은 큰 장점이고 기술의 진보입니다. 하지만 그만큼 전자의 양을 더욱 세밀하게 조절(프로그램)해야 하므로 동작 속도가 느려집니다. 또 얼마나 오랫동안 정보를 유지할 수 있느냐에 대한 신뢰성이 문제가 될 수 있다는 분명한 단점이 있습니다.

결론적으로, 삼성전자 128단 V낸드는 256Gb에 TLC 조건이니, 약 853억개(2560억/3)의 셀이 한 칩 속에 들어있다는 이야기가 되겠네요.

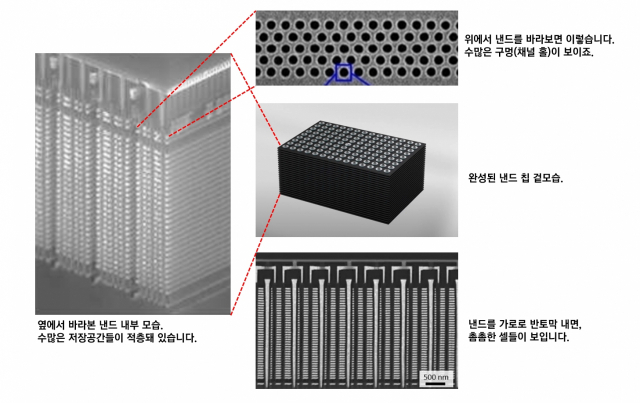

◇이제 '채널 홀'에 대해서 알아봅시다.

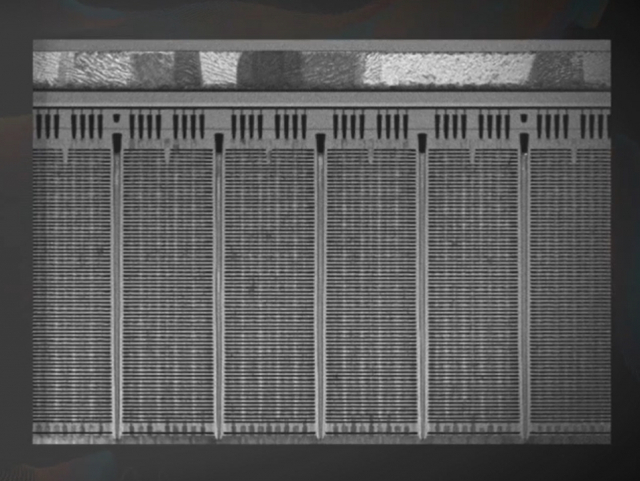

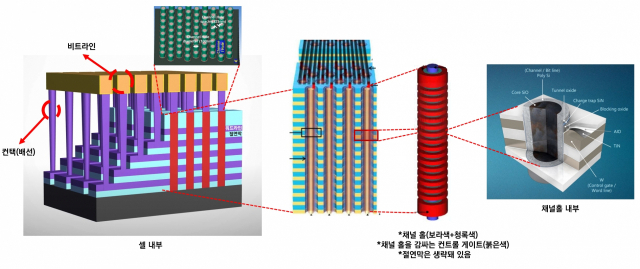

3D 낸드플래시의 백미는 '채널 홀'입니다. 삼성 128단 낸드의 경우 1층부터 128층을 관통하는 채널 홀(윗 그림 회색 구멍)이 6억7,000만개 정도 뚫려 있다고 하죠.

군대로 비유해볼까요. V낸드 칩이 사단이라면 '채널홀'은 한 개 대대입니다. 128단 낸드 사단에 6억7,000만개 대대, 각 대대에는 128개 소대(셀)가 있는 셈이죠.

숱한 낸드 보도자료에서 '채널 홀을 한번에 뚫었다'는 얘기 많이 보셨을 겁니다. 그럼 이 구멍은 어떻게 구성돼 있을까.

'구멍', '뚫었다'는 표현이 많이 나와 채널 홀 속은 마치 텅 비어있는 것 같지만 사실 전혀 그렇지 않습니다. 3D 낸드의 핵심 요소는 이 곳에 다 들어가 있거든요.

채널 홀은 '펜트하우스' 입니다. 전기 알갱이들이 128층을 오르내릴 수 있는 초고속 엘리베이터(채널)가 있고요. 전자가 엘리베이터를 내리면 도넛 모양의 독채 방이 마련돼 있어서 입니다.

그럼 좀 더 자세히 볼까요. 채널홀 속은 나무의 나이테처럼 여러 겹의 물질로 둘러싸여 채워진 모습입니다. 크게 '게이트 절연막 층(a.k.a. 실리콘 나이트라이드)'와 '채널(채널 폴리)'로 구성돼 있는데요. 이 막들을 하나씩 벗겨내 보겠습니다.

아까 말씀드렸듯 채널은 엘리베이터 역할을 합니다. 전자들이 자유롭게 이동하는 통로입니다.

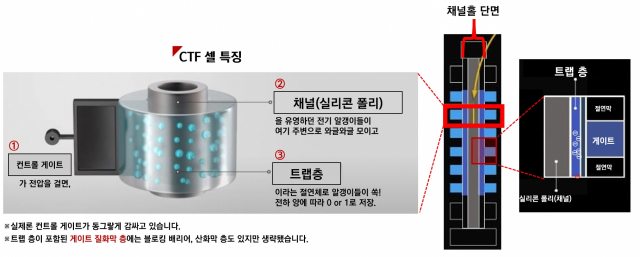

우리가 더 눈여겨봐야 할 부분은 '게이트 절연막층'입니다. 크게 △산화막△트랩층 △블로킹 배리어로 구성돼 있죠. 자, 그 중에서도 가장 중요한 포인트가 트랩층입니다. 이 층이 전기 알갱이를 저장하는 공간입니다.

오, 그런데 말입니다. 아까는 낸드 안에서 전기 알갱이가 저장되는 공간은 '플로팅 게이트'라는 이름 아니었냐고요.

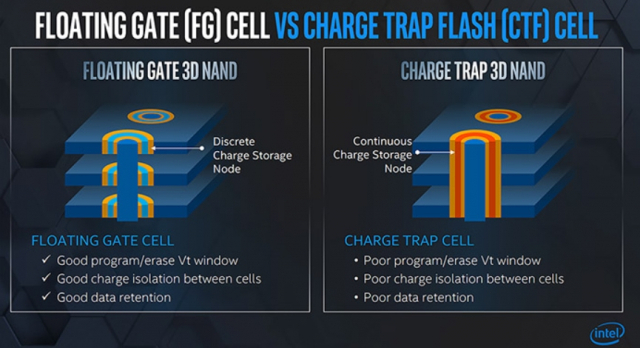

잘 보셨습니다. 지금 말씀드린 '게이트 절연막층'이 바로 플로팅 게이트의 ‘업그레이드’ 버전이거든요. 트랩 층 기반의 힙한 3D 낸드 셀 구조, 차지트랩플래시(CTF)이 여기서 등장합니다. 지난해 SK하이닉스의 인텔 낸드사업부 인수합병 발표에서 SK하이닉스는 'CTF 방식 3D 낸드'를 구현한다는 이야기 참 많이 나왔었죠.

CTF는 첨단 방식입니다. 확실히 트랩 층이 플로팅 게이트에 비해 장점이 많습니다. 아무리 절연막이 둘러싸고 있다고 해도, 플로팅 게이트는 태생 자체가 전기가 흐르는 ‘도체’ 입니다. 반면 부도체 그 자체인 트랩 층은 이웃 셀 간 간섭이 훨씬 적습니다.

또 플로팅 게이트보다 부피가 훨씬 작아서 면적 축소가 핵심인 3D 낸드 구성에도 유리합니다. CTF가 3D 낸드 데이터 저장 공간의 핵심이 되는 이유입니다.

물론 인텔 낸드사업부가 96단 3D 낸드플래시를 '플로팅 게이트' 구조로 만들었다고 지난 2019년 국내 행사를 열고 발표한 적도 있죠. 플로팅 게이트 방식이 스마트폰 등 모바일 기기 낸드 제조에 적용하기는 어렵지만, 데이터센터용 낸드 특화 기술이 될 수 있다는 설명입니다. 하지만 3D 낸드에서는 이미 CTF 방식으로 대세가 굳혀졌다는 업계 중론입니다.

다시 채널 홀에서 일어나는 일을 정리하면 이렇습니다. 채널홀 바깥에 있는 컨트롤 게이트(워드라인)에서 전압이 걸리면, 채널홀 속 채널을 유유히 돌아다니고 있던 전기 알갱이가 CTF로 이끌려서 저장됩니다. 낸드의 모든 정보 공간은 '홀' 속 얇은 막에 내재돼 있다는 것이 ‘포인트’입니다.

※2탄으로 넘어가시려면 여기를 클릭해주세요.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com