네패스라웨가 차세대 패키징 공정인 팬아웃-패널레벨패키지(FOPLP) 본격 양산에 돌입했다. 회사는 내년 생산 능력을 2배 이상 확대할 것이라고 7일 밝혔다.

네패스라웨는 7일 문승욱 산업통상자원부 장관, 이시종 충북도지사, 이병구 네패스 회장과 고객사 및 협력사 대표 등이 참석한 가운데 자사 청안캠퍼스 PLP라인의 준공식을 개최했다.

FOPLP는 반도체 후공정 업계에서 차세대 패키징 공정으로 각광받는 기술이다.

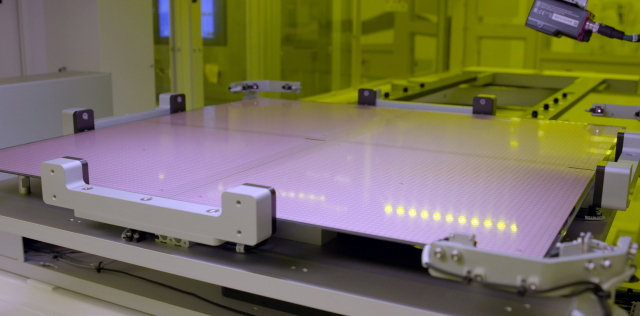

PLP는 말그대로 평평한 판(패널)에서 하는 패키징공정이다. 기존에는 동그란 웨이퍼 상태 그대로 패키징을 진행했다. 하지만 PLP는 여러 개 웨이퍼에 있는 칩들을 일정한 크기로 자르고, 대형 판에 배열한 다음 한번에 패키징하는 방법이다.

이렇게 하면 생산성이 크게 올라간다. 웨이퍼 대비 더 많은 칩을 한번에 패키징할 수 있는데다, 동그란 웨이퍼처럼 가장자리에 소재가 낭비되는 일이 없어서 원가도 절감할 수 있다.

네패스는 이런 PLP에 기판(PCB)와 각종 배선(리드프레임)을 쓰지않는 팬아웃(FO) 기법까지 덧댄 FOPLP로 공정 효율 극대화를 노리고 있다.

네패스라웨는 FOPLP를 미래 먹거리로 일찌감치 점찍고 축구장 25개 규모인 18만6,000㎡(5만6,000평) PLP 팹을 자사 청안캠퍼스에 만들었다.

이곳에서는 600㎜ 사각형 판(패널) 기준 연간 최대 9만 6,000장 이상을 생산할 수 있다. 이미 지난 3분기 고객사 인증을 마쳐 생산성은 물론 안정성까지 양산에 박차를 가하고 있다.

네패스라웨는 내년까지 청안 PLP 팹 생산 능력을 첫 양산 규모 대비 두 배 이상으로 확대할 계획이다. 이미 네패스는 내년 9월까지 1,200억원 규모의 FO-PLP 증설 투자를 완료할 것이라고 공시한 바 있다.

정 회장은 “FOPLP는 소재·부품·장비 등 국내외 파트너들과 오랫동안 협력해 온 결과로 고사양 반도체를 위한 최적의 패키징 솔루션”이라며 “네패스는 앞으로도 파트너와의 긴밀한 협력을 통해 첨단 기술의 패키징 솔루션을 제공해 나갈 것”이라고 밝혔다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com