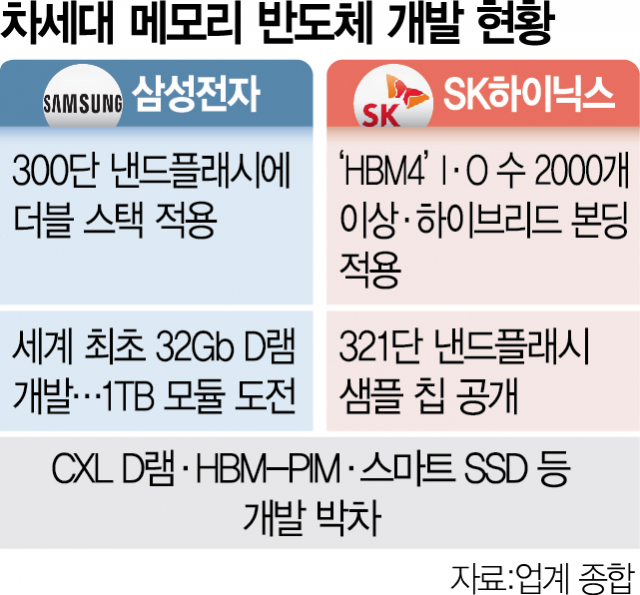

글로벌 메모리반도체 시장을 양분하고 있는 삼성전자(005930)와 SK하이닉스(000660)가 다시 한번 극한의 공정 혁신에 착수한 것으로 확인됐다. 차세대 메모리로 불리는 고대역폭메모리(HBM)는 물론 낸드플래시 분야에서도 끊임없는 기술 진화를 통해 경쟁 업체와의 초격차를 유지한다는 전략이다.

4일 반도체 업계에 따르면 삼성전자와 SK하이닉스는 2026년 양산 계획인 6세대 ‘HBM4’에 입출력(I·O) 수를 2000개 이상으로 늘리는 방안을 추진하고 있다.

I·O는 반도체 칩 속에서 정보가 드나드는 통로인데 개수가 많을수록 그래픽처리장치(GPU) 등 프로세서와 HBM 간 정보 교류가 훨씬 빨라진다. 2013년 세계 첫 HBM부터 현재 개발된 HBM 5세대(HBM3E)까지 I·O 수는 칩당 1024개다. 2000개가 넘는 I·O를 가진 HBM은 아직 공개된 적이 없다. 또한 국제반도체표준협의기구(JEDEC)에서 추진 중인 차기 HBM I·O 수 표준화에 선제 대응하는 움직임이기도 하다.

I·O 수가 늘면 공정 난도도 올라간다. 그러나 양사는 100%에 가까운 HBM 수율에 자신감을 갖고 주도권 굳히기에 들어간 것으로 알려졌다.

낸드 시장의 독보적 1위인 삼성전자 역시 누구도 따라오기 힘든 기술 확보에 공을 들이고 있다. 삼성전자는 내년 양산할 9세대 300단 이상 V낸드에 더블스택 공정을 채택하기로 했다. 더블스택은 낸드를 두 번에 나눠서 만든 뒤 한 개 칩으로 결합하는 방법을 뜻한다. 라이벌 낸드플래시 업체는 300단 이상 낸드를 총 세 번에 걸쳐 생산한 뒤 합치는 ‘트리플스택’을 도입하는 추세다. 더블스택은 트리플스택보다 기술적 난도가 높다. 그러나 생산시간과 공정 수, 원자재를 대폭 줄일 수 있어 원가 절감에 상당히 유리하다.

국내 반도체 업계가 막대한 투자가 필요한 공정 혁신에 나선 데는 ‘메모리 1위’에 자만하다 순식간에 시장을 내줄 수 있다는 절박한 위기감이 작용했다. 미국 마이크론테크놀로지와 중국 최대의 메모리 회사인 YMTC 등이 정부 지원을 등에 업고 ‘타도 한국’을 외치고 있다. 반도체 업계의 한 관계자는 “해외 반도체 기업들이 한국의 기술 경쟁력을 단번에 따라잡기는 쉽지 않다”면서도 “기존 제품군에서는 끊임없는 공정 혁신으로 격차를 벌리고 컴퓨트익스프레스링크(CXL), 프로세스인메모리(PIM) 등 미래 메모리 시장에 대한 강력한 투자를 이어가야 한다”고 강조했다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com